# Expressing Flexibility in Logic Synthesis by Boolean Relations

Anna Bernasconi Università di Pisa, Italy

#### Overview

- Classic applications

- Multilevel logic optimization

- Approximate Logic Synthesis

- Bounded-depth logic synthesis via Boolean relations

- Bi-decomposed Circuits

- Synthesis with critical signals: P-circuits

# Multilevel logic optimization

Given a multilevel logic network, obtain an **equivalent** representation of the network, **optimal** w.r.t. a cost function involving area and delay

- identifying subnetworks to be optimized,

- deriving their flexibility

- and replacing such subnetworks by simpler, optimized ones

#### SINGLE-OUTPUT SUBNETWORKS

The flexibility for implementing the node's function can be represented by don't cares

# Multilevel logic optimization

Given a multilevel logic network, obtain an **equivalent** representation of the network, **optimal** w.r.t. a cost function involving area and delay

- identifying subnetworks to be optimized,

- deriving their flexibility

- and replacing such subnetworks by simpler, optimized ones

#### SINGLE-OUTPUT SUBNETWORKS

The flexibility for implementing the node's function can be represented by don't cares

#### Multi-output subnetworks

Don't cares are not sufficient for representing all the flexibility

Don't care-based methods allow us to optimize only *one* single-output subnetwork at a time

#### Boolean relations describe all the flexibility

Boolean relations allow the simultaneous modification of all nodes of a subnetwork

# Minimization of a *two-bit adder* due to the filtering effect of a *comparator* [Brayton, Somenzi, 1989]

$$z = 01 \Rightarrow a + b < 3$$

$z = 00 \Rightarrow (a + b = 3) \lor (a + b = 4)$

$z = 10 \Rightarrow a + b > 4$ .

Input values can be partitioned into three equivalence classes:

Values less than 3: {000, 001, 010} Values equal to 3 or 4: {011, 100} Values greater than 4: {101, 110, 111}

The values in each class are not distinghished by the comparator

# Minimization of a *two-bit adder* due to the filtering effect of a *comparator* [Brayton, Somenzi, 1989]

$$z = 01 \Rightarrow a + b < 3$$

$z = 00 \Rightarrow (a + b = 3) \lor (a + b = 4)$

$z = 10 \Rightarrow a + b > 4$ .

Input values can be partitioned into three equivalence classes:

Values less than 3: {000, 001, 010} Values equal to 3 or 4: {011, 100} Values greater than 4: {101, 110, 111}

The values in each class are not distinghished by the comparator

We can change the output value of the adder, to any other value in the same equivalence class.

#### Boolean relation describing the flexible adder

| $a_1a_0b_1b_0$                                 | $x_2 x_1 x_0$   |

|------------------------------------------------|-----------------|

| {0000,0001,0010,0100,1000,0101}                | {000,001,010}   |

| $\{0011, 0110, 1001, 1010, 1100, 0111, 1101\}$ | {011, 100}      |

| $\{1011, 1110, 1111\}$                         | {101, 110, 111} |

# Minimization of a *two-bit adder* due to the filtering effect of a *comparator* [Brayton, Somenzi, 1989]

Minimization with don't cares including the normal adder as an acceptable implementation

| $a_1 a_0 b_1 b_0$ | $x_2 x_1 x_0$ |

|-------------------|---------------|

| 11-0              | 0 1 1         |

| - 1 1 0           | 0 1 1         |

| 10-1              | 011           |

| -011              | 011           |

| - 111             | 100           |

| 11-1              | 100           |

| 111-              | 010           |

| 1 - 1 -           | 100           |

Minimization of the Boolean relation much simpler minimum solution

| $a_1a_0b_1b_0$ | $x_2 x_1 x_0$ |

|----------------|---------------|

| 0 - 1 -        | 0 1 0         |

| 1 - 0 -        | 010           |

| 1 - 1 -        | 100           |

| 1              | 001           |

| - 1            | 001           |

# Approximate Logic Synthesis (ALS)

- Exploit error tolerance of applications to implement approximate designs with

- smaller area

- smaller delay

- or lower energy consumption

- Modify some outputs of a function, so that the produced error is tolerable

# Approximate Logic Synthesis (ALS)

- Exploit error tolerance of applications to implement approximate designs with

- smaller area

- smaller delay

- or lower energy consumption

- Modify some outputs of a function, so that the produced error is tolerable

#### Error frequency

number of minterms on which an error occurs, as a fraction of the total number of minterms

#### Error magnitude

maximum amount by which the numerical value at the outputs of a function can deviate from the exact value

### ALS and Boolean Relations

#### [Miao, Gerstlauer, Orshansky, 2013]:

- ALS under arbitrary error magnitude and error frequency constraints

- Two-level logic minimization algorithm, two-phase approach:

- derive the solution of the problem constrained only by the magnitude of errors

the solution is iteratively refined to meet the original error frequency constraint

### ALS and Boolean Relations

[Miao, Gerstlauer, Orshansky, 2013]:

- ALS under arbitrary error magnitude and error frequency constraints

- Two-level logic minimization algorithm, two-phase approach:

- ◆ derive the solution of the problem constrained only by the magnitude of errors

→ expressed and solved using Boolean relations

the solution is iteratively refined to meet the original error frequency constraint

# ALS constrained by Error Magnitude only

- Multi-output function  $f: \{0,1\}^n \to \{0,1\}^k$

- *M*: constrain on the magnitude of possible errors

#### PROBLEM

Find  $f': \{0,1\}^n \to \{0,1\}^k$  of **minimal cost** s.t.

$$\forall x \in \{0,1\}^n \quad |f(x) - f'(x)| \le M$$

# ALS constrained by Error Magnitude only

- Multi-output function  $f: \{0,1\}^n \to \{0,1\}^k$

- M: constrain on the magnitude of possible errors

#### PROBLEM

Find  $f': \{0,1\}^n \to \{0,1\}^k$  of **minimal cost** s.t.

$$\forall x \in \{0,1\}^n \quad |f(x) - f'(x)| \le M$$

•  $\forall x \in \{0,1\}^n$ , e(x) = output error set for xadditional values that the function can take while satisfying the error magnitude constraint

$$\mathcal{R}_{f'}(x) \in \{f(x) \cup e(x)\}$$

each input corresponds to more than one output: f' becomes a Boolean relation  $\mathcal{R}_{f'}$

$\Rightarrow$  minimize the Boolean relation  $\mathcal{R}_{f'}$ , under a given metric (i.e., the number of literals in a SOP representation)

## Adder

| $x_1 x_2$ | $f(x_1,x_2)$ |

|-----------|--------------|

| 00        | 00           |

| 01        | 01           |

| 10        | 01           |

| 11        | 10           |

$$L(f) = 6$$

$$SOP(f^{(1)}) = x_1x_2$$

$SOP(f^{(2)}) = \overline{x}_1x_2 + x_1\overline{x}_2$

#### Adder

| $x_1 x_2$ | $f(x_1,x_2)$ |

|-----------|--------------|

| 0 0       | 00           |

| 01        | 01           |

| 10        | 01           |

| 11        | 10           |

$$L(f) = 6$$

$$SOP(f^{(1)}) = x_1x_2$$

$SOP(f^{(2)}) = \overline{x}_1x_2 + x_1\overline{x}_2$

## Adder, M=1

| $x_1 x_2$ | $\mathcal{R}_{f'}(x_1,x_2)$ |

|-----------|-----------------------------|

| 00        | {00,01}                     |

| 01        | {01,00,10}                  |

| 10        | {01,00,10}                  |

| 11        | {10,01,11}                  |

#### Adder

| $x_1 x_2$ | $f(x_1,x_2)$ |

|-----------|--------------|

| 0 0       | 00           |

| 01        | 01           |

| 10        | 01           |

| 11        | 10           |

|           |              |

$$L(f) = 6$$

$$SOP(f^{(1)}) = x_1x_2$$

$SOP(f^{(2)}) = \overline{x}_1x_2 + x_1\overline{x}_2$

### Adder, M=1

$$\begin{array}{c|cc} x_1 \, x_2 & \mathcal{R}_{f'}(x_1, x_2) \\ \hline 0 \, 0 & \{00, 01\} \\ 0 \, 1 & \{01, 00, 10\} \\ 1 \, 0 & \{01, 00, 10\} \\ 1 \, 1 & \{10, 01, 11\} \\ \end{array}$$

$$L(f')=0$$

$$SOP(f^{(1)}) = 0$$

$SOP(f^{(2)}) = 1$

#### Adder

| $x_1 x_2$ | $f(x_1,x_2)$ |

|-----------|--------------|

| 00        | 00           |

| 01        | 01           |

| 10        | 01           |

| 11        | 10           |

$$L(f) = 6$$

$$SOP(f^{(1)}) = x_1x_2$$

$SOP(f^{(2)}) = \overline{x}_1x_2 + x_1\overline{x}_2$

### Adder, M=1

$$\begin{array}{c|cccc} x_1 \, x_2 & \mathcal{R}_{f'}(x_1, x_2) \\ \hline 0 \, 0 & \{00, 01\} & \textbf{X} \\ 0 \, 1 & \{01, 00, 10\} \\ 1 \, 0 & \{01, 00, 10\} \\ 1 \, 1 & \{10, 01, 11\} & \textbf{X} \\ \end{array}$$

$$L(f')=0$$

$$SOP(f^{(1)}) = 0$$

$SOP(f^{(2)}) = 1$

Error frequency: 50 %

# Frequency constrained ALS algorithm

- The BR solution may not satisfy the constrain on error frequency

- Iterative and greedy algorithm for systematically corrects the wrong outputs (leading to the smallest cost increase) until the error frequency constraint is met

# Frequency constrained ALS algorithm

- The BR solution may not satisfy the constrain on error frequency

- Iterative and greedy algorithm for systematically corrects the wrong outputs (leading to the smallest cost increase) until the error frequency constraint is met

| ERROR FRI                                   | EQUENCY:     | 25 %                        |   |

|---------------------------------------------|--------------|-----------------------------|---|

| <i>x</i> <sub>1</sub> <i>x</i> <sub>2</sub> | $f(x_1,x_2)$ | $\mathcal{R}_{f'}(x_1,x_2)$ |   |

| 0.0                                         | 00           | {00, <mark>01</mark> }      | X |

| 01                                          | 01           | { <mark>01</mark> , 00, 10} |   |

| 10                                          | 01           | { <mark>01</mark> , 00, 10} |   |

| 11                                          | 10           | $\{10, 01, 11\}$            | X |

| '                                           | l            |                             |   |

|                                             |              |                             |   |

|                                             |              |                             |   |

|                                             |              |                             |   |

|                                             |              |                             |   |

# Frequency constrained ALS algorithm

- The BR solution may not satisfy the constrain on error frequency

- Iterative and greedy algorithm for systematically corrects the wrong outputs (leading to the smallest cost increase) until the error frequency constraint is met

| Error frequency: 25 %                            |                                             |              |                             |

|--------------------------------------------------|---------------------------------------------|--------------|-----------------------------|

|                                                  | <i>x</i> <sub>1</sub> <i>x</i> <sub>2</sub> | $f(x_1,x_2)$ | $\mathcal{R}_{f'}(x_1,x_2)$ |

|                                                  | 00                                          | 00           | {00,01}                     |

|                                                  | 01                                          | 01           | { <mark>01</mark> , 00, 10} |

|                                                  | 10                                          | 01           | { <mark>01</mark> , 00, 10} |

|                                                  | 11                                          | 10           | {10, 01, 11} X              |

| L(f')=2                                          |                                             |              |                             |

| $SOP(f^{(1)}) = 0$<br>$SOP(f^{(2)}) = x_1 + x_2$ |                                             |              |                             |

# Bounded-depth logic synthesis via Boolean relations: Bi-Decomposition (joint work with R. K. Brayton, V.Ciriani, G. Trucco, and T. Villa)

$$f:\{0,1\}^n o \{0,1,-\}$$

$f=(f_{on},f_{dc},f_{off})$  can be covered with

- → a SOP derived by the on-set (+ some dc-points)

- ightarrow a POS resulting from the complement of a SOP for the off-set (+ some dc-points)

- ★ Which one gives the best cover, the SOP or the POS form?

- \* Can we study a form that is part in SOP and part in POS form, and is better than both?

# Bounded-depth logic synthesis via Boolean relations: Bi-Decomposition (joint work with R. K. Brayton, V.Ciriani, G. Trucco, and T. Villa)

$$f: \{0,1\}^n \to \{0,1,-\}$$

$f = (f_{on}, f_{dc}, f_{off})$  can be covered with

- $\rightarrow$  a SOP derived by the on-set (+ some dc-points)

- ightarrow a POS resulting from the complement of a SOP for the off-set (+ some dc-points)

- \* Which one gives the best cover, the SOP or the POS form?

- \* Can we study a form that is part in SOP and part in POS form, and is better than both?

We propose a **bi-decomposed form** that is part in SOP form and part in POS

$$f_B = \overline{f_0}$$

op  $f_1$

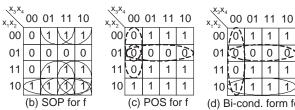

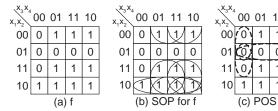

# Bounded-depth logic synthesis via Boolean relations: **Bi-Decomposition**

| $X_3X_4$<br>$X_1X_2$ | 00 | 01 | 11 | 10 |  |

|----------------------|----|----|----|----|--|

| 00                   | 0  | 1  | 1  | 1  |  |

| 01                   | 0  | 0  | 0  | 0  |  |

| 11                   | 0  | 1  | 1  | 1  |  |

| 10                   | 1  | 1  | 1  | 1  |  |

| (a) f                |    |    |    |    |  |

•

$$f_{SOP} = f_1^{SOP} = x_1 \overline{x}_2 + x_1 x_3 + x_1 x_4 + \overline{x}_2 x_3 + \overline{x}_2 x_4$$

10 literals

•

$$f_{POS} = \overline{f}_0^{POS} = (x_1 + \overline{x}_2)(x_1 + x_3 + x_4)(\overline{x}_2 + x_3 + x_4)$$

8 literals

# Bounded-depth logic synthesis via Boolean relations: **Bi-Decomposition**

•

$$f_{SOP} = f_1^{SOP} = x_1 \overline{x}_2 + x_1 x_3 + x_1 x_4 + \overline{x}_2 x_3 + \overline{x}_2 x_4$$

10 literals

•

$$f_{POS} = \overline{f}_0^{POS} = (x_1 + \overline{x}_2)(x_1 + x_3 + x_4)(\overline{x}_2 + x_3 + x_4)$$

8 literals

•

$$f_B = \overline{f}_0 + f_1 = ((x_1 + \overline{x}_2)(x_3 + x_4)) + x_1 \overline{x}_2$$

6 literals

1000 is in the the OFF set of  $\overline{f}_0$  and in the ON set of  $f_1$ thus is in the ON set of the  $\overline{f}_0 + f_1$

## Synthesis of Bi-decomposed Circuits and Boolean relations

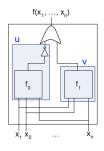

$$f:\{0,1\}^n \to \{0,1,-\}, \qquad f = u \text{ op } v \qquad \qquad u \leftarrow \overline{f_0}, \ v \leftarrow f_1$$

**Inputs** of u and v: the same as the inputs of f:  $x_1, \ldots, x_n$ **Output**: is the output that **op** takes on  $u(x_1, \ldots, x_n)$  and  $v(x_1, \ldots, x_n)$

## Synthesis of Bi-decomposed Circuits and Boolean relations

$$f:\{0,1\}^n \to \{0,1,-\}, \qquad f = u \text{ op } v \qquad \qquad u \leftarrow \overline{f_0}, \ v \leftarrow f_1$$

$$f = u \mathbf{op} v$$

$$u \leftarrow \overline{f_0}, \ v \leftarrow f_1$$

**Inputs** of u and v: the same as the inputs of f:  $x_1, \ldots, x_n$

**Output**: is the output that **op** takes on  $u(x_1, ..., x_n)$  and  $v(x_1, ..., x_n)$

#### AND GROUP

$$\begin{array}{c|c} u \ v & \mathsf{AND} \\ \hline u \ v & \not= \\ u \ \overline{v} & \not\Rightarrow \\ \hline u \ \overline{v} & \mathsf{NOR} \end{array}$$

### OR GROUP

| $u + v$ $\overline{u} + v$ $u + \overline{v}$ $\overline{u} + \overline{v}$ | OR            |

|-----------------------------------------------------------------------------|---------------|

| $\overline{u} + v$                                                          | $\Rightarrow$ |

| $u + \overline{v}$                                                          | <=            |

| $\overline{u} + \overline{v}$                                               | NAND          |

|                                                                             |               |

#### XOR GROUP

$$u \oplus v \mid XOR$$

$u \overline{\oplus} v \mid XNOR$

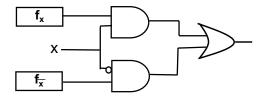

## Synthesis of Bi-decomposed Circuits and Boolean relations

$$f:\{0,1\}^n \to \{0,1,-\}, \hspace{1cm} f=u \hspace{1cm} extbf{op} \hspace{1cm} v \hspace{1cm} u \leftarrow \overline{f_0}, \hspace{1cm} v \leftarrow f_1$$

**Inputs** of u and v: the same as the inputs of  $f: x_1, \ldots, x_n$

**Output**: is the output that **op** takes on  $u(x_1, \ldots, x_n)$  and  $v(x_1, \ldots, x_n)$

# $\begin{array}{c|c} AND GROUP \\ u v & AND \\ \overline{u} v & \not= \\ u \overline{v} & \not\Rightarrow \\ \overline{u} \overline{v} & NOR \end{array}$

- The two-input operator induces flexibility that cannot be expressed exactly by don't care conditions only: a Boolean relation is required

- For each binary **op**, we define  $\mathcal{R}_{op}: \{0,1\}^n \to \{0,1\}^2$  s.t.

- the set of functions compatible with  $\mathcal{R}_{op}$  corresponds to the set of pairs (u, v) occurring in all bi-decomposed circuit implementations of f w.r.t. op.

- an optimal solution of  $\mathcal{R}_{op}$  is an optimal bi-decomposed circuit for f

## Construction of $\mathcal{R}_{OR}$

•  $\forall x \in f_{on}$ , x must be associated to one of the three output values on which u + v evaluates to 1

$$\mathcal{R}_{OR}(x) = \{01, 10, 11\} = \{1-, -1\}$$

•  $\forall x \in f_{off}$ , x must be associated to the output 00 on which u + v evaluates to 0

$$\mathcal{R}_{OR}(x) = 00$$

•  $\forall x \in f_{dc}$ , x can be associated to any output

$$\mathcal{R}_{OR}(x) = \{--\}$$

# Construction of $\mathcal{R}_{op}$

#### **AND** table

|                 | $\mathcal{R}_{\mathit{AND}}$ | $\mathcal{R}_{ eq}$ | $\mathcal{R}_{\mathit{NOR}}$ | $\mathcal{R}_{\not\Rightarrow}$ |

|-----------------|------------------------------|---------------------|------------------------------|---------------------------------|

| $x \in f_{on}$  | {11}                         | {01}                | {00}                         | {10}                            |

| $x \in f_{off}$ | $\{0-,-0\}$                  | $\{1-, -0\}$        | $\{1-,-1\}$                  | $  \{0-,-1\}  $                 |

| $x \in f_{dc}$  | {}                           | {}                  | {}                           | {}                              |

#### **OR** table

|                 | $\mathcal{R}_{\mathit{OR}}$ | $\mathcal{R}_{\Rightarrow}$ | $\mathcal{R}_{\mathit{NAND}}$ | $\mathcal{R}_{\Leftarrow}$ |

|-----------------|-----------------------------|-----------------------------|-------------------------------|----------------------------|

| $x \in f_{on}$  | $\{1-,-1\}$                 | $\{0-,-1\}$                 | $\{0-,-0\}$                   | [1-,-0]                    |

| $x \in f_{off}$ | {00}                        | {10}                        | {11}                          | {01}                       |

| $x \in f_{dc}$  | {}                          | {}                          | {}                            | {}                         |

#### **XOR** table

|                 | $\mathcal{R}_{	extit{XNOR}}$ | $\mathcal{R}_{\mathit{XOR}}$ |

|-----------------|------------------------------|------------------------------|

| $x \in f_{on}$  | $\{00, 11\}$                 | $\{01, 10\}$                 |

| $x \in f_{off}$ | $\{01, 10\}$                 | $\{00, 11\}$                 |

| $x \in f_{dc}$  | {}                           | {}                           |

# Construction of $\mathcal{R}_{op}$

The three tables are distinguished by whether

- the offset is partitioned (AND group)

- the onset is partitioned (OR group)

- or both are partitioned (XOR group)

How this partitioning is done is task of the *Boolean relation* minimizer

# Construction of $\mathcal{R}_{op}$

The three tables are distinguished by whether

- the offset is partitioned (AND group)

- the **onset** is partitioned **(OR group)**

- or both are partitioned (XOR group)

How this partitioning is done is task of the *Boolean relation minimizer*

Bi-decomposed circuit minimization problem  $\iff$  problem of finding an optimal implementation of  $\mathcal{R}_{op}$

Good gains in a majority of benchmarks against affordable increases in synthesis time

# Synthesis with critical signals: P-circuits (joint work with V. Ciriani, G. Trucco, and T. Villa)

#### **Scenario**

- Logic synthesis in presence of critical signals that should be moved toward the output

- signals with high switching activity

- $\rightarrow$  for decreasing power consumption

- late arriving signals

- ightarrow for decreasing circuit delay

# Synthesis with critical signals: P-circuits

(joint work with V. Ciriani, G. Trucco, and T. Villa)

#### **Scenario**

- Logic synthesis in presence of critical signals that should be moved toward the output

- signals with high switching activity

- $\rightarrow$  for decreasing power consumption

- late arriving signals

- ightarrow for decreasing circuit delay

#### PROBLEM

Restructure (or synthesize) a circuit in order to move critical signals near to the output (decreasing the cone of influence)

- minimizing the circuit area

- keeping the number of levels bounded

- performing an efficient minimization

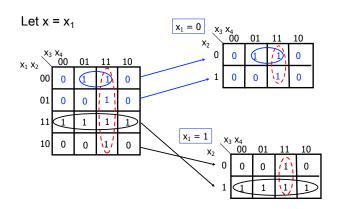

# Simple solution: Shannon decomposition

x is the critical signal

$$f = \overline{x} f_{|x=0} + x f_{|x=1}$$

- the cofactors  $f_{|x=0}$  and  $f_{|x=1}$  do not depend on x

- x is near to the output

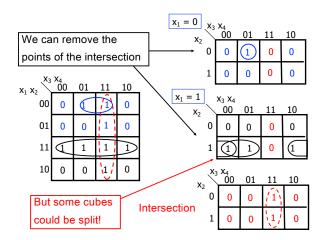

# Problem of Shannon approach

# Problem of Shannon approach

It is not a compact representation

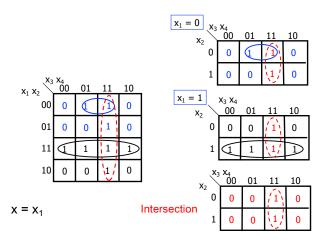

### Decomposition with intersection

- try not to split the cubes

- let the critical signal near to the output

#### IDEA

- the cubes that do not depend on x and cross the two sets are not projected

- how to identify these cubes?

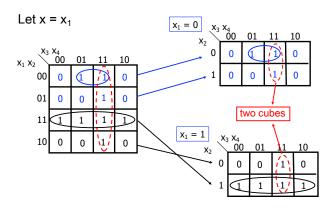

#### Decomposition with intersection

- try not to split the cubes

- let the critical signal near to the output

#### IDEA

- the cubes that do not depend on x and cross the two sets are not projected

- how to identify these cubes?

They are in the intersection between the two cofactors

$$I=f_{|x_i=0}\cap f_{|x_i=1}$$

• keep / unprojected, and project only the minterms in  $f_{|x_1=0} \setminus I$  and  $f_{|x_2=1} \setminus I$

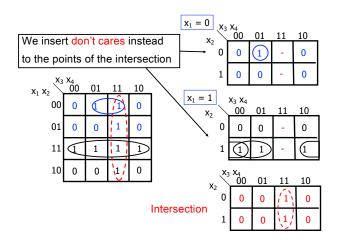

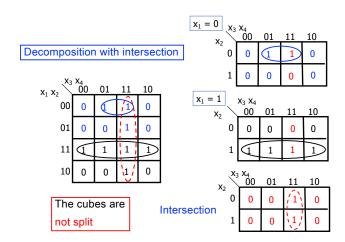

### P-circuits for completely specified functions

- if a point is in I and is useful for a better minimization of f<sub>|xi=0</sub> and f<sub>|xi=1</sub>,

it can be kept both in the cofactors and in the intersection

- if a point is covered in both the projected cofactors, it is not necessary to cover it in I (replaced by a don't care in I)

## P-circuits for completely specified functions

- if a point is in I and is useful for a better minimization of f<sub>|xi=0</sub> and f<sub>|xi=1</sub>,

it can be kept both in the cofactors and in the intersection

- if a point is covered in both the projected cofactors, it is not necessary to cover it in I (replaced by a don't care in I)

#### P-CIRCUIT

A P-circuit of a completely specified function f is the circuit

$$P(f) = \overline{x}_i f^{=} + x_i f^{\neq} + f^{I}$$

- **6** P(f) = f

# Minimization of P-circuits using Boolean Relation

Find the sets  $f^{=}, f^{\neq}, f^{I}$  leading to a **P-circuit of minimal cost**

- $f: \{0,1\}^n \to \{0,1\}$   $\mathcal{R}_f: \{0,1\}^{n-1} \to \{0,1\}^3$

- Input set for  $\mathcal{R}_f$ : all input variables but the critical signal  $x_i$

- Output set for  $\mathcal{R}_f$ : all triple of functions  $f^=, f^{\neq}, f^I$  defining a P-circuit for f

# Minimization of P-circuits using Boolean Relation

Find the sets  $f^{=}, f^{\neq}, f^{I}$  leading to a **P-circuit of minimal cost**

- $f: \{0,1\}^n \to \{0,1\}$   $\mathcal{R}_f: \{0,1\}^{n-1} \to \{0,1\}^3$

- Input set for  $\mathcal{R}_f$ : all input variables but the critical signal  $x_i$

- Output set for  $\mathcal{R}_f$ : all triple of functions  $f^=, f^{\neq}, f^I$  defining a P-circuit for f

| $X_1 \dots X_{i-1} X_{i+1} \dots X_n$ | $\mathcal{R}_f = (f^=, f^{\neq}, f^I)$ |

|---------------------------------------|----------------------------------------|

| points in $f_{ x_i =0} \setminus I$   | {100}                                  |

| points in $f_{ x_i=1} \setminus I$    | {010}                                  |

| points in I                           | $\{1, 11-\}$                           |

| all other points                      | {000}                                  |

## Minimization of P-circuits using Boolean Relation

Find the sets  $f^{=}, f^{\neq}, f^{I}$  leading to a **P-circuit of minimal cost**

- $f: \{0,1\}^n \to \{0,1\}$   $\mathcal{R}_f: \{0,1\}^{n-1} \to \{0,1\}^3$

- Input set for  $\mathcal{R}_f$ : all input variables but the critical signal  $x_i$

- Output set for  $\mathcal{R}_f$ : all triple of functions  $f^-, f^+, f^-$  defining a P-circuit for f

| $X_1 \dots X_{i-1} X_{i+1} \dots X_n$ | $\mathcal{R}_f = (f^=, f^{\neq}, f^I)$ |

|---------------------------------------|----------------------------------------|

| points in $f_{ x_i=0} \setminus I$    | {100}                                  |

| points in $f_{ x_i=1} \setminus I$    | {010}                                  |

| points in I                           | $\{1, 11-\}$                           |

| all other points                      | {000}                                  |

#### ${ m Theorem}$

P-circuit minimization for f

minimization of the Boolean relation  $\mathcal{R}_f$

P-circuits minimized with Boolean relations are more compact than P-circuits expressed and minimized as incompletely specified functions

#### Conclusions

- Boolean relations can be extremely useful for modeling Boolean hard optimization problems

- → with Boolean relations we can model problems that cannot be completely described with incompletely specified functions

- Problem: scalability of the approach

- Boolean relation minimization is a very hard problem

- Boolean relation minimizers cannot handle relations with many outputs

- Boolean relations have been successfully used in logic synthesis to solve problems that can be cast as the minimization of relations with a constant number of outputs (2, 3)

#### THANK YOU