# SAT in Logic Synthesis

### Mathias Soeken

Integrated Systems Laboratory, EPFL, Switzerland

### Background

SAT-based area recovery in structural technology mapping

Applying logic synthesis to speedup SAT

SAT-based exact synthesis: encodings, topology families, and parallelism

## Background

SAT-based area recovery in structural technology mapping

Applying logic synthesis to speedup SAT

SAT-based exact synthesis: encodings, topology families, and parallelisn

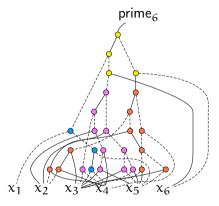

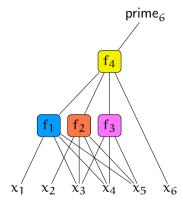

$\mathsf{prime}_6 = [(x_6 x_5 \dots x_1)_2 \text{ is prime}]$

1. Represent function as simple logic network with small gate primitives (here: And-inverter graph)

- 1. Represent function as simple logic network with small gate primitives (here: And-inverter graph)

- 2. Cover network with subnetworks with limited fanin size k (here k = 3 and k = 4)

- 1. Represent function as simple logic network with small gate primitives (here: And-inverter graph)

- 2. Cover network with subnetworks with limited fanin size k (here k = 3 and k = 4)

- 1. Represent function as simple logic network with small gate primitives (here: And-inverter graph)

- 2. Cover network with subnetworks with limited fanin size k (here k = 3 and k = 4)

- 3. Collapse covered subnetworks into lookup-table nodes

### Background

SAT-based area recovery in structural technology mapping

Applying logic synthesis to speedup SAT

SAT-based exact synthesis: encodings, topology families, and parallelism

▶ Input: Logic network, set of k-cuts for each gate

- ▶ Input: Logic network, set of k-cuts for each gate

- ► Output: k-LUT mapping

- ▶ Input: Logic network, set of k-cuts for each gate

- ► Output: k-LUT mapping

- ➤ Solve problem "Does there exist a k-LUT mapping with L cuts?" as a SAT problem.

- ▶ Input: Logic network, set of k-cuts for each gate

- Output: k-LUT mapping

- ➤ Solve problem "Does there exist a k-LUT mapping with L cuts?" as a SAT problem.

- ➤ Solve problem starting from some satisfiable upper bound, and improve bound until no more solution can be found

- ► Input: Logic network, set of k-cuts for each gate

- Output: k-LUT mapping

- ➤ Solve problem "Does there exist a k-LUT mapping with L cuts?" as a SAT problem.

- ➤ Solve problem starting from some satisfiable upper bound, and improve bound until no more solution can be found

- Result guaranteed to be optimum for selected cuts

- ► Input: Logic network, set of k-cuts for each gate

- Output: k-LUT mapping

- ➤ Solve problem "Does there exist a k-LUT mapping with L cuts?" as a SAT problem.

- Solve problem starting from some satisfiable upper bound, and improve bound until no more solution can be found

- Result guaranteed to be optimum for selected cuts

- How to encode the problem?

- ► Input: Logic network, set of k-cuts for each gate

- Output: k-LUT mapping

- ➤ Solve problem "Does there exist a k-LUT mapping with L cuts?" as a SAT problem.

- ➤ Solve problem starting from some satisfiable upper bound, and improve bound until no more solution can be found

- Result guaranteed to be optimum for selected cuts

- How to encode the problem?

- How to make it reliably efficient for large networks?

### **Variables**

m<sub>i</sub> = [gate i is mapped]

for each gate i

#### **Variables**

- m<sub>i</sub> = [gate i is mapped]

for each gate i

- ▶ s<sub>i,C</sub> = [cut C is selected for gate i] for each cut C of gate i

#### **Variables**

- m<sub>i</sub> = [gate i is mapped]

for each gate i

- s<sub>i,C</sub> = [cut C is selected for gate i]

for each cut C of gate i

#### Clauses

▶ (m₀) for each gate o that drives an output

#### **Variables**

- m<sub>i</sub> = [gate i is mapped]

for each gate i

- s<sub>i,C</sub> = [cut C is selected for gate i]

for each cut C of gate i

#### Clauses

- ▶ (m₀) for each gate o that drives an output

- $\blacktriangleright \ m_i \to \bigvee_{C \in \text{CUTS}(i)} s_{i,C} \ \text{for each gate } i$

#### **Variables**

- m<sub>i</sub> = [gate i is mapped]

for each gate i

- s<sub>i,C</sub> = [cut C is selected for gate i]

for each cut C of gate i

#### Clauses

- (m<sub>o</sub>) for each gate o that drives an output

- $\blacktriangleright \ m_i \to \bigvee_{C \in \text{CUTS}(i)} s_{i,C}$  for each gate i

- $ightharpoonup s_{i,C} o \bigwedge_{j \in C} \mathfrak{m}_j$  for each cut C of gate i

#### **Variables**

- m<sub>i</sub> = [gate i is mapped]

for each gate i

- s<sub>i,C</sub> = [cut C is selected for gate i]

for each cut C of gate i

#### Clauses

- (m<sub>o</sub>) for each gate o that drives an output

- $\blacktriangleright \ m_i \to \bigvee_{C \in \text{CUTS}(i)} s_{i,C} \ \text{for each gate } i$

- $\blacktriangleright \ s_{i,C} \to \bigwedge_{j \in C} m_j$  for each cut C of gate i

- $ightharpoonup \sum m_i \leqslant L$

▶ Runtime degrades quickly as networks become larger

- ▶ Runtime degrades quickly as networks become larger

- ► Restrict network size using windowing (to, e.g., 128 gates)

- Runtime degrades quickly as networks become larger

- ► Restrict network size using windowing (to, e.g., 128 gates)

- ▶ Windowing is applied to mapped network, not cutting through mapped cuts

- Runtime degrades quickly as networks become larger

- Restrict network size using windowing (to, e.g., 128 gates)

- ▶ Windowing is applied to mapped network, not cutting through mapped cuts

- Find good pivots to extract windows

- Runtime degrades quickly as networks become larger

- Restrict network size using windowing (to, e.g., 128 gates)

- Windowing is applied to mapped network, not cutting through mapped cuts

- Find good pivots to extract windows

- Cache windows to avoid duplicate optimization effort

### **ABC**

► Command &satlut

### **ABC**

- ► Command &satlut

- ► Input must be 6-LUT mapped AIG

### **ABC**

- ► Command &satlut

- ► Input must be 6-LUT mapped AIG

#### mockturtle

► C++ function satlut\_mapping<Ntk>

#### **ABC**

- ► Command &satlut

- ► Input must be 6-LUT mapped AIG

#### mockturtle

- ► C++ function satlut\_mapping<Ntk>

- Works on arbitrary logic networks

#### **ABC**

- ► Command &satlut

- ► Input must be 6-LUT mapped AIG

#### mockturtle

- ► C++ function satlut\_mapping<Ntk>

- Works on arbitrary logic networks

- Works on arbitrary cut sizes

#### **ABC**

- ► Command &satlut

- ► Input must be 6-LUT mapped AIG

#### mockturtle

- ► C++ function satlut\_mapping<Ntk>

- Works on arbitrary logic networks

- Works on arbitrary cut sizes

- ▶ Not fully finished (PR #122)

Background

SAT-based area recovery in structural technology mapping

Applying logic synthesis to speedup SAT

SAT-based exact synthesis: encodings, topology families, and parallelisn

### CNF generation for logic networks

➤ SAT-based verification and synthesis tasks require logic network to be represented as CNF e.g., equivalence checking, model checking, Boolean resubstitution

### CNF generation for logic networks

- ➤ SAT-based verification and synthesis tasks require logic network to be represented as CNF e.g., equivalence checking, model checking, Boolean resubstitution

- ► Traditional approach is to use Tseytin's encoding

- ➤ SAT-based verification and synthesis tasks require logic network to be represented as CNF e.g., equivalence checking, model checking, Boolean resubstitution

- ► Traditional approach is to use Tseytin's encoding

- ► Each gate is assigned an auxiliary variable

- ➤ SAT-based verification and synthesis tasks require logic network to be represented as CNF e.g., equivalence checking, model checking, Boolean resubstitution

- ► Traditional approach is to use Tseytin's encoding

- ► Each gate is assigned an auxiliary variable

- Gate function is transformed into CNF

- ➤ SAT-based verification and synthesis tasks require logic network to be represented as CNF e.g., equivalence checking, model checking, Boolean resubstitution

- ► Traditional approach is to use Tseytin's encoding

- ► Each gate is assigned an auxiliary variable

- Gate function is transformed into CNF

- ightharpoonup Example  $c = a \wedge b$ :

$$(a \vee \bar{c})(b \vee \bar{c})(\bar{a} \vee \bar{b} \vee c)$$

- ➤ SAT-based verification and synthesis tasks require logic network to be represented as CNF e.g., equivalence checking, model checking, Boolean resubstitution

- ► Traditional approach is to use Tseytin's encoding

- ► Each gate is assigned an auxiliary variable

- Gate function is transformed into CNF

- ightharpoonup Example  $c = a \wedge b$ :

$$(a \lor \bar{c})(b \lor \bar{c})(\bar{a} \lor \bar{b} \lor c)$$

► Advantage: Resulting CNF is linear in the number of gates

- ➤ SAT-based verification and synthesis tasks require logic network to be represented as CNF e.g., equivalence checking, model checking, Boolean resubstitution

- ► Traditional approach is to use Tseytin's encoding

- ► Each gate is assigned an auxiliary variable

- Gate function is transformed into CNF

- ightharpoonup Example  $c = a \wedge b$ :

$$(a \lor \bar{c})(b \lor \bar{c})(\bar{a} \lor \bar{b} \lor c)$$

- ► Advantage: Resulting CNF is linear in the number of gates

- Disadvantage: Requires the use of many auxiliary variables

▶ Perform LUT mapping to control tradeoff between number of auxiliary variables and number of clauses

- ▶ Perform LUT mapping to control tradeoff between number of auxiliary variables and number of clauses

- ▶ Idea: perform Tseytin encoding on LUTs, not on gates

- ► Perform LUT mapping to control tradeoff between number of auxiliary variables and number of clauses

- ▶ Idea: perform Tseytin encoding on LUTs, not on gates

- Advantage: Number of auxiliary variables corresponds to number of mapped gates

- ► Perform LUT mapping to control tradeoff between number of auxiliary variables and number of clauses

- ▶ Idea: perform Tseytin encoding on LUTs, not on gates

- Advantage: Number of auxiliary variables corresponds to number of mapped gates

- ► Cost function based on CNF size

- ▶ Perform LUT mapping to control tradeoff between number of auxiliary variables and number of clauses

- Idea: perform Tseytin encoding on LUTs, not on gates

- Advantage: Number of auxiliary variables corresponds to number of mapped gates

- Cost function based on CNF size

- May even lead to fewer number of overall clauses

Background

SAT-based area recovery in structural technology mapping

Applying logic synthesis to speedup SAT

SAT-based exact synthesis: encodings, topology families, and parallelism

# SAT in Logic Synthesis

#### Mathias Soeken

Integrated Systems Laboratory, EPFL, Switzerland